AD生成PCB时出现报错如何解决?

作者

AD生成PCB报错:工程师实战排查指南

设计图完美通过检查,点击“生成PCB”的瞬间,红色的错误提示却刺眼地弹出——相信每一位使用Altium Designer的工程师都经历过这种挫败,AD生成PCB过程中的报错并非无解难题,关键在于精准定位和系统解决,本文将结合常见故障场景,提供清晰的排查路径。

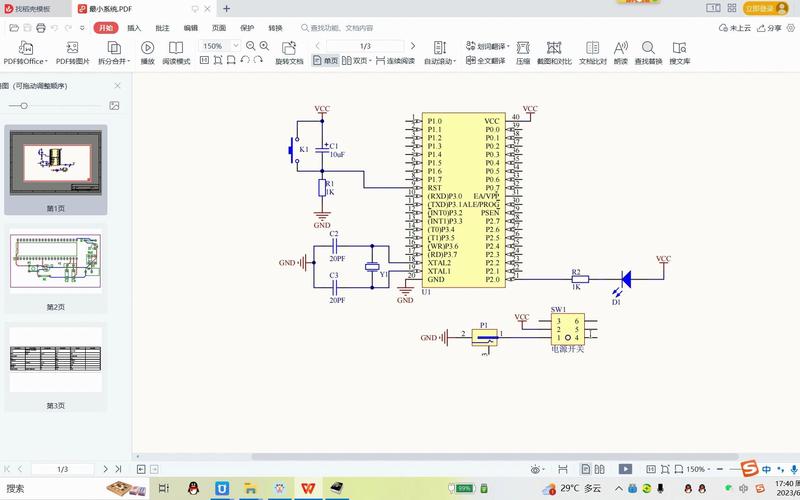

原理图根源:不可忽视的起点

许多PCB报错的种子,早在原理图阶段就已埋下:

- 网络标识缺失或冲突: 最常见的是网络标签(Net Label)未正确放置或命名冲突,某次项目中,一个关键电源网络标签被无意中覆盖,导致整组电源网络在PCB中消失,务必使用“Navigator”面板交叉检查原理图与PCB的网络连通性,确保每个网络都清晰无误。

- 器件未正确关联封装: 原理图符号必须指向有效的PCB封装(Footprint),当出现“Footprint Not Found”时,需检查:库路径是否在软件设置中正确添加?封装名称是否完全匹配?尤其注意第三方库或老旧库的兼容性问题,养成在放置元件前,双击确认封装信息的习惯。

- 端口与图纸入口问题: 在多图纸设计中,Port(端口)和Sheet Entry(图纸入口)必须严格配对,常见错误是端口类型(如Input/Output/Bidirectional)不匹配,或命名存在大小写、空格差异,使用“Project > Component Links…”功能强制检查关联性。

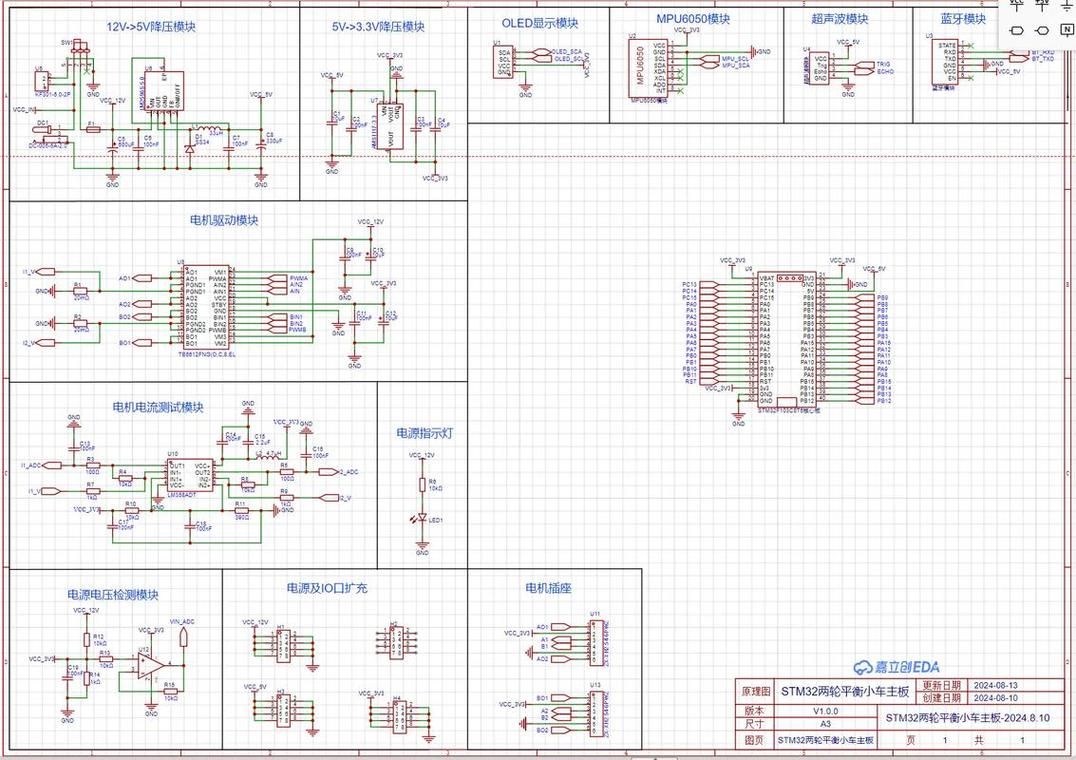

封装库陷阱:细节决定成败

封装错误直接导致PCB布局无法进行或生产灾难:

- 焊盘与原理图引脚不匹配: 原理图符号引脚编号(Designator)必须与封装焊盘编号一一对应,一个二极管符号若引脚定义为A/K,而封装焊盘编号是1/2,导入PCB时必然报错,仔细核对或使用AD的封装向导确保一致性。

- 焊盘层定义错误: 表面贴装(SMT)器件的焊盘应仅定义在顶层(Top Layer)或底层(Bottom Layer),误包含多层(Multi-Layer)会导致生产问题,通孔(THT)器件焊盘则必须为Multi-Layer。

- 原点偏移与3D模型问题: 封装原点(通常设在器件中心或引脚1)若偏离太远,拖放器件时会异常“飞走”,复杂的3D模型未正确关联或存在破面,也可能在更新PCB时报错,使用“Tools > Manage 3D Bodies for Component”检查。

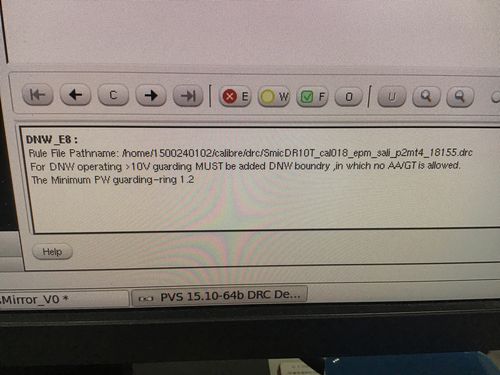

设计规则冲突:规则的刚性约束

AD的设计规则(Design Rules)是PCB生成的硬性门槛:

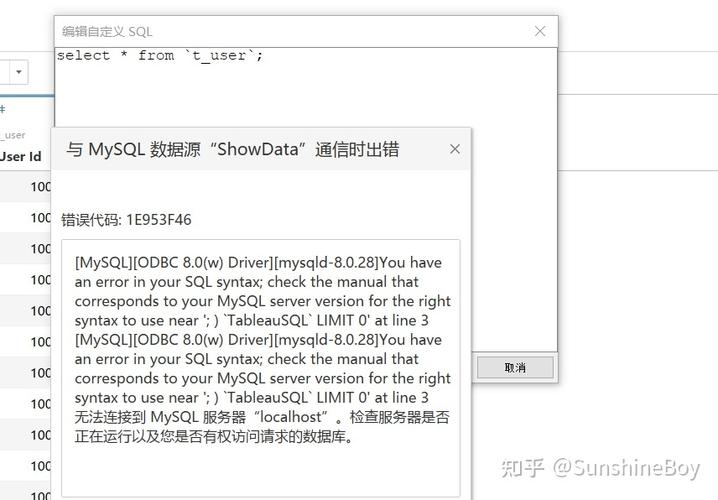

- 间距规则(Clearance): 这是报错重灾区,尤其当元件密集或走线复杂时,极易违反铜箔间、焊盘间、过孔间的最小安全距离,需检查规则是否合理(如高压部分间距需加大),或布局布线是否存在疏忽。

- 布线宽度规则(Width): 电源线、地线通常需要更大线宽,若规则中定义了特定网络(如12V、GND)的最小/最大宽度,而实际布线未达标,必然报错,在“PCB Rules and Constraints Editor”中仔细核对。

- 掩膜与锡膏规则(Solder Mask, Paste Mask): 阻焊层开窗过小可能导致焊接困难,开窗过大则可能引起短路,需确保规则设置符合板厂工艺能力(咨询板厂获取推荐值)。

- 未布线网络(Un-Routed Net): 这是最直接的错误——仍有鼠线(飞线)未完成物理连接,使用“Tools > Un-Routed Net”高亮显示,逐一排查是遗漏布线还是规则限制导致无法布通。

高效排查与修复流程

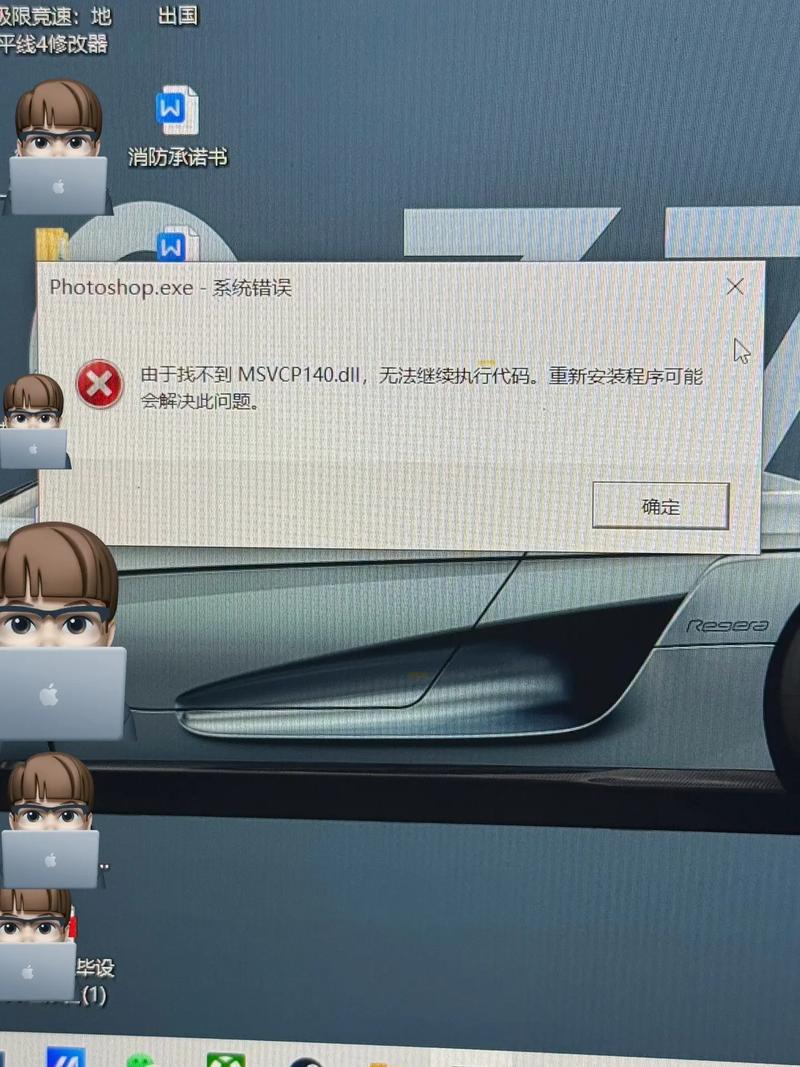

- 读懂错误信息: 不要被满屏红色吓退,AD的错误报告会明确列出错误类型(如“Un-Routed Net Constraint”)、涉及对象(网络名、元件标号)和所在规则,这是解决问题的第一线索。

- 利用交叉探测(Cross Probe): 在PCB错误列表或规则冲突详情中,右键点击错误项,选择“Cross Probe”,软件会自动跳转并高亮显示PCB或原理图中的问题点,极大提升定位效率。

- 分层检查规则: 在规则编辑器中,规则按优先级排序,检查是否低优先级规则(如All对象)意外覆盖了高优先级规则(如特定网络Net Class),理解规则的继承与覆盖关系。

- 活用Room与器件类: 对于布局有特殊要求的区域(如高速区、模拟区),可创建Room并对其应用特定规则(如更小间距、线宽),将同类器件(如所有BGA)归入器件类(Component Class),统一设置扇出规则。

- ECO工程变更的必要性: 当原理图修改后(如增删元件、改变网络),必须通过“Design > Update PCB Document…”执行ECO变更,严格检查变更列表,确认无误后再执行,避免手动在PCB上直接修改导致原理图与PCB不同步,这是后续错误的根源。

设计习惯决定效率: 严谨的原理图绘制、规范统一的库管理、清晰分层的规则设置,是最大限度避免生成报错的核心,每次报错都是对设计规范性的检验,也是提升设计可靠性的契机,与其在错误弹出后匆忙救火,不如在源头构建更健壮的设计流程——这是减少AD生成PCB报错最根本的方法,每一次对规则的敬畏,终将转化为电路板稳定运行的底气。

资深硬件工程师李明回忆道:“最棘手的报错往往源于一个被忽略的原理图端口,凌晨三点盯着满屏红色错误,才深刻理解AD规则检查的严格不是刁难,而是对产品质量的守护,现在团队强制要求原理图符号和封装的双人复核,PCB报错率下降了70%。”

目录